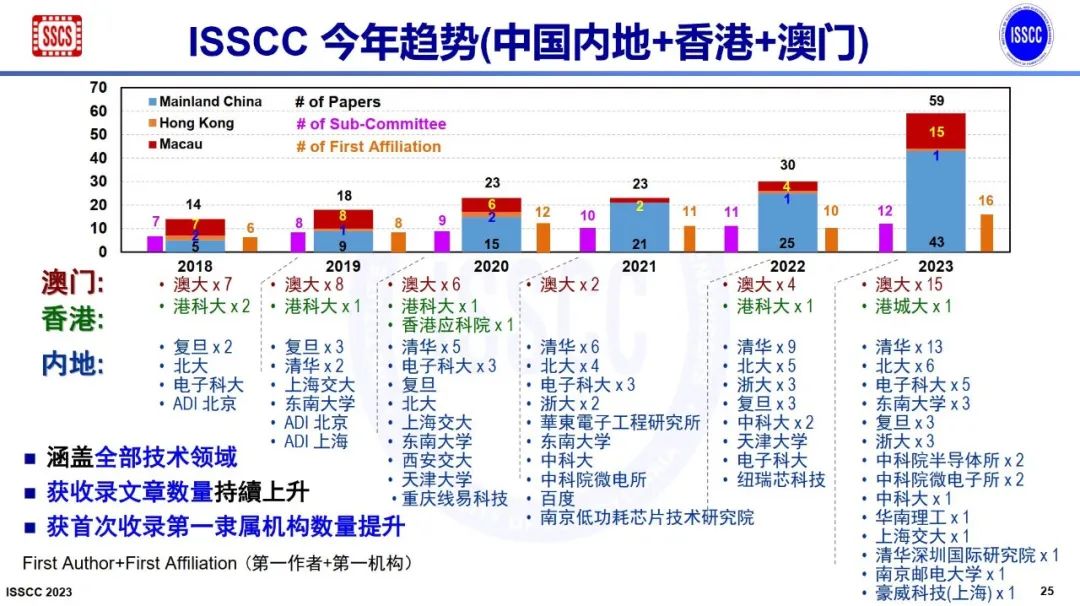

被业界誉为芯片设计界的国际奥林匹克盛会的国际固态电路大会(ISSCC 2023)近日在美国旧金山举行。今年恰逢ISSCC 70周年大庆,也是自2020年疫情以来首次全线下模式召开的芯片设计领域的国际盛会,来自全球工业界与学术界的数千名领域专家齐聚旧金山。本次大会,清华大学电子工程系教授、长江学者、湃方科技首席科学家刘勇攀团队的两项高能效端侧AI加速芯片技术成功入围。 边缘计算技术是新一代智能物联网技术驱动引擎。高效的边缘计算技术有利于算力的去中心化,从而有效地增加物联网端侧的功能范围,实现更高效、更及时、更可靠的端侧计算。湃方科技团队长期致力于硬件与算法联合优化的技术路线,研发了Sticker系列、tritium 103等多种端侧AI加速芯片,覆盖稀疏量化、变换域加速、差分加速、近似计算、存内计算等多项技术维度,7次入选ISSCC大会。本次团队再次入选,标志着相关技术的新突破。 论文介绍:

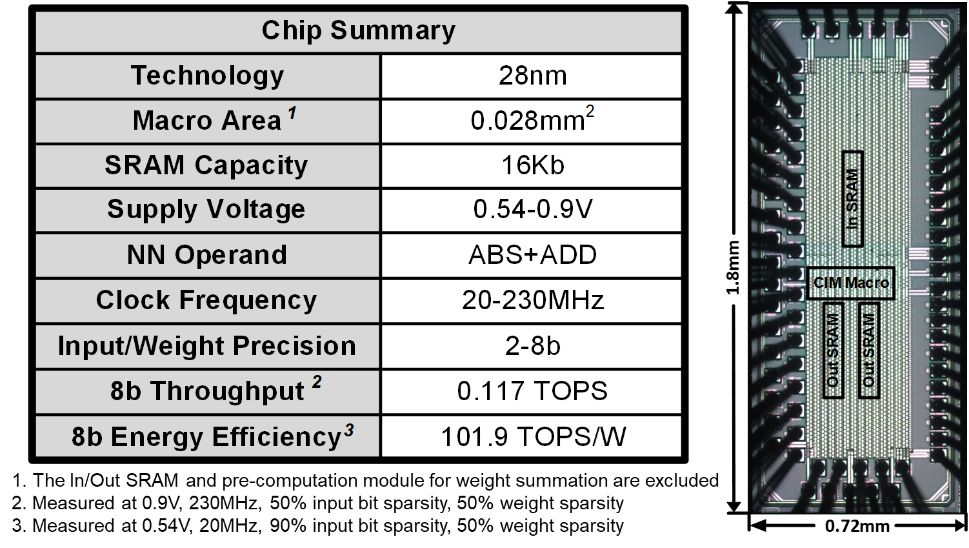

刘勇攀、贾弘洋、杨华中教授等发表题为“A 28-nm 38-to-102-TOPS/W 8-b Multiply-less Approximate Digital SRAM Compute-In-Memory Macro for Neural-Network Inference”的论文。数字存内计算技术相比于模拟存内计算具有高精度、易集成的特点,但其能量效率和面积效率受数字乘累加电路限制难以进一步提升。针对该关键问题,研究团队设计并流片验证了一款基于SRAM的高能效近似数字存内计算芯片。该芯片采用加法网络近似传统卷积网络,通过L1距离代替乘法运算,大幅削减了数字电路开销。同时采用预计算重塑数据流,将绝对值计算进一步简化为比较操作。此外,设计的高密度动态逻辑比较器通过电路级的可约束近似计算进一步提升能效和面积效率。基于以上创新点设计的存内计算芯片采用28nm工艺制造,峰值8比特计算能量效率达到102TOPS/W,相比于相同工艺下数字存内计算工作能效提升3倍以上,展示了近似数字存内计算电路的性能优势。

存内计算核心芯片及硬件指标

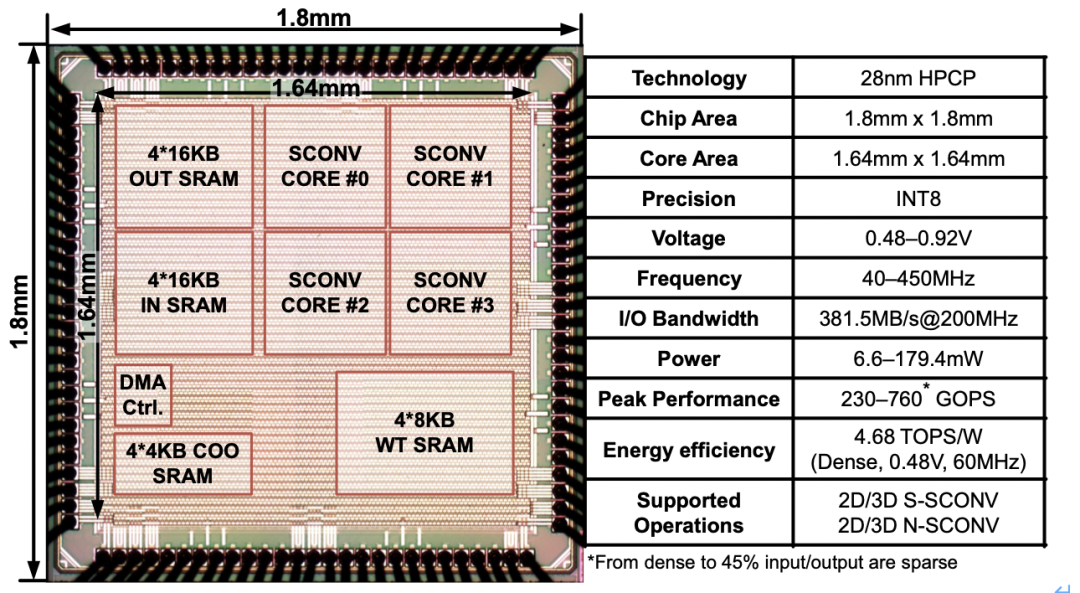

刘勇攀、杨华中教授等发表题为“A 28nm 2D/3D Unified Sparse Convolution Accelerator with Block-Wise Neighbor Searcher for Large-Scaled Voxel-Based Point Cloud Network”的论文。相比2D视觉信息,3D点云数据可以提供丰富的几何、形状和深度信息,使得深度3D点云模型在自动驾驶、智能机器人等领域得到广泛应用。然而3D点云数据具备稀疏、非规则的分布特性,带来随机数据存取访问、2D/3D多样稀疏卷积计算、非均衡计算核心调度等硬件难题,限制其面向实际应用落地。为提升点云模型的硬件运行效率,研究团队设计并发布了2D/3D融合的稀疏点云加速器芯片。团队基于分块存储管理机制实现无序稀疏数据的连续、高效传输,设计2D/3D多稀疏度可重构卷积计算电路实现4类稀疏卷积的高效支持,提出多核心混合调度优化策略解决稀疏计算存在的负载不均衡、数据复用效率低的问题。该芯片是首款支持大规模化点云模型端到端运行的智能芯片,在TSMC 28nm工艺下成功流片,峰值处理能效达到4.68TOPS/W,相比2022年文献中的相关工作能效提升2倍以上。同时团队将该芯片与激光雷达集成实现了可演示实时系统,并在ISSCC Demo环节中进行展出,显示出其对点云模型强大的实时推理能力。

点云加速器芯片及硬件指标